# Timing analysis / pipelining

V1.0

- Overview of timing report generated by Vivado

- How pipelining can improve you timings

- Workshop

#### **Franck Jullien**

@fjullien06

https://github.com/fjullien

### Report file - check\_timing\_report

- \*\_timing.rpt

- check\_timing report → error report

Can be ignored most of the time

```

Table of Contents

1. checking no clock (0)

2. checking constant clock (0)

3. checking pulse width clock (0)

4. checking unconstrained internal endpoints (0)

5. checking no input delay (8)

6. checking no output delay (4)

7. checking multiple clock (0)

8. checking generated clocks (0)

9. checking loops (0)

10. checking partial input delay (0)

11. checking partial output delay (0)

12. checking latch loops (0)

```

UG906 - Design Analysis and Closure Techniques

# **Report file - Design Timing Summary**

- ► WNS → Worst Negative Setup slack

- WHS → Worst Hold Slack

- WNS and WHS must be greater than or equal to zero

```

WNS(ns)

-----

-0.755

```

```

TNS(ns) TNS Failing Endpoints TNS Total Endpoints WHS(ns) THS(ns) ... -4.588 10 146 0.263 0.000 ...

```

Most influenced by your design

### **Report file - Max Delay Paths**

```

Max Delay Paths

-0.755ns (required time - arrival time)

Slack (VIOLATED) :

xilinxmultiregimpl0 regs1 reg/C

Source:

(rising edge-triggered cell FDRE clocked by clk100

Destination:

b reg[29]/D

(rising edge-triggered cell FDRE clocked by clk100

Path Group:

clk100

Path Type:

Setup (Max at Slow Process Corner)

10.000ns (clk100 rise@10.000ns - clk100 rise@0.000ns)

Requirement:

Data Path Delay:

10.790ns (logic 7.724ns (71.586%) route 3.066ns (28.414%))

Logic Levels:

(CARRY4=3 DSP48E1=2 LUT3=1 LUT6=1)

Clock Path Skew:

-0.039ns (DCD - SCD + CPR)

Destination Clock Delay (DCD):

4.795 \text{ns} = (14.795 - 10.000)

Source Clock Delay

(SCD):

5.093ns

0.259ns

Clock Pessimism Removal (CPR):

0.035 \text{ns} ((TSJ<sup>2</sup> + TIJ<sup>2</sup>)<sup>1</sup>/2 + DJ) / 2 + PE

Clock Uncertainty:

Total System Jitter (TSJ):

0.071ns

(TIJ):

Total Input Jitter

0.000ns

Discrete Jitter

(DJ):

0.000ns

Phase Error

(PE):

0.000ns

```

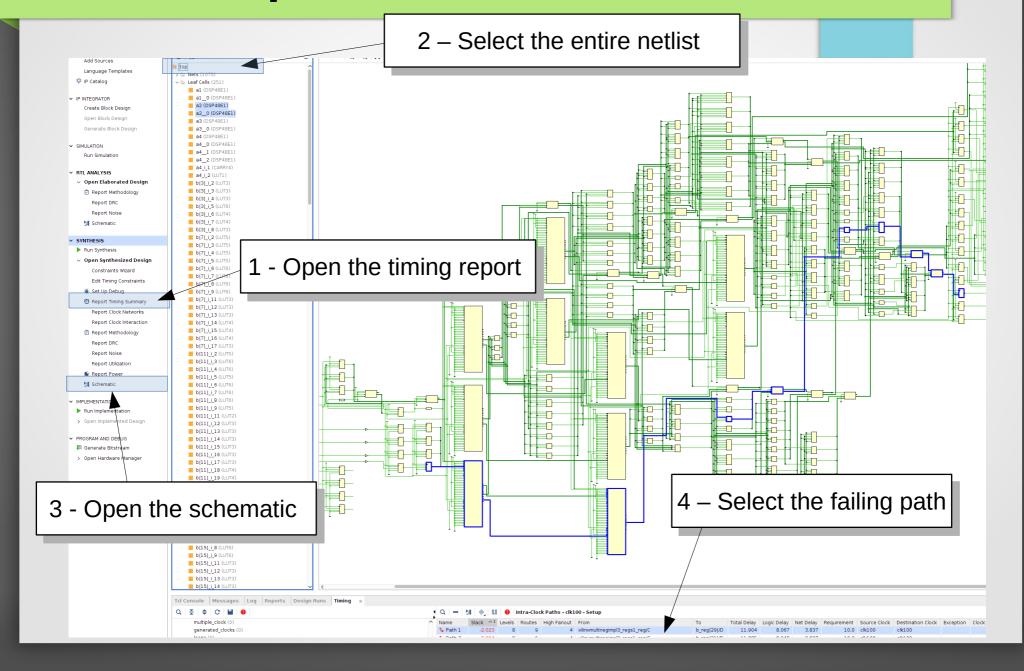

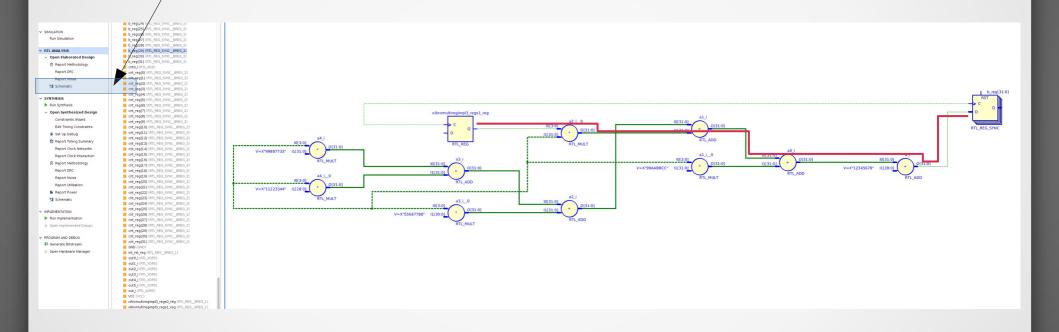

#### Visual inspection

# Visual inspection

Open the elaborated schematic

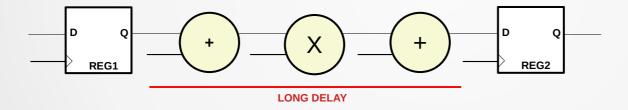

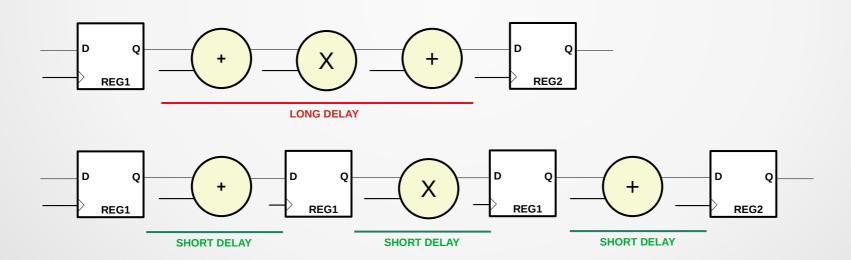

# **Pipelining**

- Long combinatorial path can be cut into smallest chunks

- We insert registers to cut combinatorial path

- Latency is introduced

### **Pipelining**

- Long combinatorial path can be cut into smallest chunks

- We insert registers to cut combinatorial path

- Latency is introduced

#### Workshop - extra0

- Build the non pipelined version of workshop\_extra0

- Look at the timing report, open Vivado and look at the RTL schematics

- Design the pipelined version of workshop\_extra0

- Make sure it works :)

- Look at the timing report, open Vivado and look at the RTL schematics